#### TENTATIVE TOSHIBA MOS DIGITAL INTEGRATED CIRCUIT SILICON MONOLITHIC

2,097,152-WORDS  $\times$  4 BANKS  $\times$  16-BITS SYNCHRONOUS DYNAMIC RAM 4,194,304-WORDS  $\times$  4 BANKS  $\times$  8-BITS SYNCHRONOUS DYNAMIC RAM 8,388,608-WORDS  $\times$  4 BANKS  $\times$  4-BITS SYNCHRONOUS DYNAMIC RAM

#### **DESCRIPTION**

TC59SM716AFT/AFTL is a CMOS synchronous dynamic random access memory organized as 2,097,152-words  $\times$  4 banks  $\times$  16 bits and TC59SM708AFT/AFTL is organized as 4,194,304 words  $\times$  4 banks  $\times$  8 bits and TC59SM704AFT/AFTL is organized as 8,388,608 words  $\times$  4 banks  $\times$  4 bits. Fully synchronous operations are referenced to the positive edges of clock input and can transfer data up to 143M words per second. These devices are controlled by commands setting. Each bank are kept active so that DRAM core sense amplifiers can be used as a cache. The refresh functions, either Auto Refresh or Self Refresh are easy to use. By having a programmable Mode Register, the system can choose the most suitable modes which will maximize its performance. These devices are ideal for main memory in applications such as work-stations.

#### **FEATURES**

| PARAMETER        |                                               | TC59SM716/M708/M704 |        |       |  |  |  |

|------------------|-----------------------------------------------|---------------------|--------|-------|--|--|--|

|                  |                                               | -70                 | -75    | -80   |  |  |  |

| t <sub>CK</sub>  | Clock Cycle Time (min)                        | 7 ns                | 7.5 ns | 8 ns  |  |  |  |

| t <sub>RAS</sub> | Active to Precharge Command Period (min)      | 42 ns               | 45 ns  | 48 ns |  |  |  |

| t <sub>AC</sub>  | Access Time from CLK (max)                    | 5.4 ns              | 5.4 ns | 6 ns  |  |  |  |

| t <sub>RC</sub>  | Ref/Active to Ref/Active Command Period (min) | 57 ns               | 65 ns  | 68 ns |  |  |  |

| I <sub>CC1</sub> | Operation Current (max) (Single bank)         | 80 mA               | 75 mA  | 70 mA |  |  |  |

| I <sub>CC4</sub> | Burst Operation Current (max)                 | 100 mA              | 95 mA  | 90 mA |  |  |  |

| I <sub>CC6</sub> | Self-Refresh Current (max)                    | 2 mA                | 2 mA   | 2 mA  |  |  |  |

| G:               | DataSheet4U.com                               |                     |        |       |  |  |  |

Single power supply of  $3.3 \text{ V} \pm 0.3 \text{ V}$

• Up to 143 MHz clock frequency

• Synchronous operations: All signals referenced to the positive edges of clock

• Architecture: Pipeline

Organization

TC59SM716AFT/AFTL:  $2,097,152 \text{ words} \times 4 \text{ banks} \times 16 \text{ bits}$  TC59SM708AFT/AFTL:  $4,194,304 \text{ words} \times 4 \text{ banks} \times 8 \text{ bits}$  TC59SM704AFT/AFTL:  $8,388,608 \text{ words} \times 4 \text{ banks} \times 4 \text{ bits}$

Programmable Mode registerAuto Refresh and Self Refresh

Burst Length: 1, 2, 4, 8, Full page

• <u>CAS</u> Latency: 2, 3

Single Write Mode

- Burst Stop Function

- Byte Data Controlled by L-DQM, U-DQM (TC59SM716)

- 4K Refresh cycles/64 ms

• Interface: LVTTL

• Package

TC59SM716AFT/AFTL: TSOPII54-P-400-0.80B TC59SM708AFT/AFTL: TSOPII54-P-400-0.80B TC59SM704AFT/AFTL: TSOPII54-P-400-0.80B

980910EBA

• TOSHIBA is continually working to improve the quality and the reliability of its products. Nevertheless, semiconductor devices in general can malfunction or fail due to their inherent electrical sensitivity and vulnerability to physical stress. It is the responsibility of the buyer, when utilizing TOSHIBA products, to observe standards of safety, and to avoid situations in which a malfunction or failure of a TOSHIBA product could cause loss of human life, bodily injury or damage to property. In developing your designs, please ensure that TOSHIBA products are used within specified operating ranges as set forth in the most recent products specifications. Also, please keep in mind the precautions and conditions set forth in the TOSHIBA Semiconductor Reliability Handbook.

• The products described in this document are subject to the foreign exchange and foreign trade laws.

The information contained herein is presented only as a guide for the applications of our products. No responsibility is assumed by TOSHIBA CORPORATION for any infringements of intellectual property or other rights of the third parties which may result from its use. No license is granted by implication or otherwise under any intellectual property or other rights of TOSHIBA CORPORATION or others.

The information contained herein is subject to change without notice.

www.DataSheet4U.com

DataShe

2000-02-08 1/49

ataSheet4

### PIN NAMES

|                          |                                   | _                                     |

|--------------------------|-----------------------------------|---------------------------------------|

| A0~A11                   | Address                           |                                       |

| BS0, BS1                 | Bank Select                       | ]   ,                                 |

| DQ0~DQ3<br>(TC59SM704)   |                                   | Vcc Vc                                |

| DQ0~DQ7<br>(TC59SM708)   | Data Input/Output                 | DQ0 DQ<br>Vccq Vcc<br>DQ1 N<br>DQ2 DQ |

| DQ0~DQ15<br>(TC59SM716)  |                                   | Vssq Vss<br>DQ3 N<br>DQ4 DQ           |

| CS                       | Chip Select                       | Vccq Vcc<br>DQ5 N                     |

| RAS                      | Row Address Strobe                | DQ6 DQ<br>Vssq Vss<br>DQ7 N           |

| CAS                      | Column Address Strobe             | Vcc Vc<br>LDQM N                      |

| WE                       | Write Enable                      | WE W<br>CAS CA                        |

| DQM<br>(TC59SM708/M704)  | Output Dischlandwite Mask         | RAS RA<br>CS C<br>BS0 BS<br>BS1 BS    |

| UDQM/LDQM<br>(TC59SM716) | Output Disable/Write Mask         | A10/AP A10/A<br>A0 A<br>A1 A          |

| CLK                      | Clock inputs                      | A2 A<br>A3 A                          |

| CKE                      | Clock enable                      | Vcc Vc                                |

| V <sub>CC</sub>          | Power (+3.3 V)                    |                                       |

| V <sub>SS</sub>          | Ground                            |                                       |

| Vccq                     | Power (+3.3 V)<br>(for DQ buffer) | ataSheet4U.com                        |

| V <sub>SSQ</sub>         | Ground<br>(for DQ buffer)         |                                       |

| NC                       | No Connection                     |                                       |

### PIN ASSIGNMENT (TOP VIEW)

DataShe

et4U.com

www.DataSheet4U.com

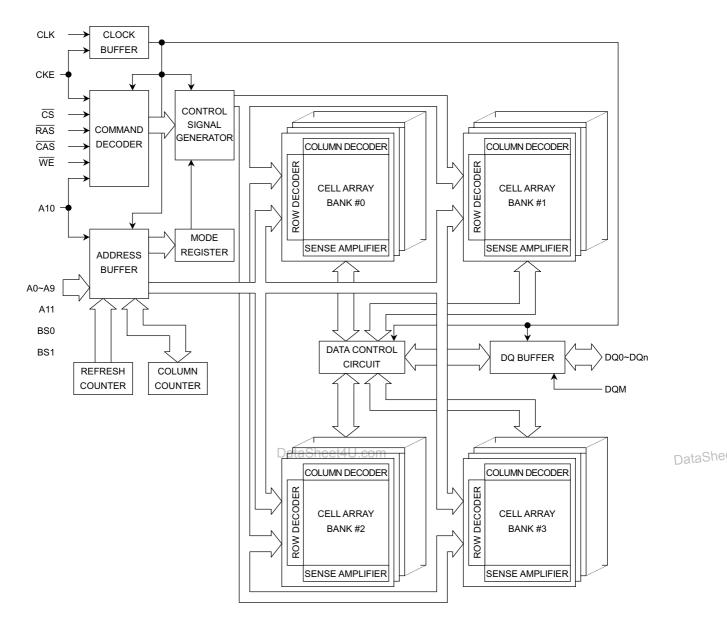

### **BLOCK DIAGRAM**

NOTE: The TC59SM704AFT/AFTL configuration is  $4096 \times 2048 \times 4$  of cell array with the DQ pins numbered DQ0~DQ3. The TC59SM708AFT/AFTL configuration is  $4096 \times 1024 \times 8$  of cell array with the DQ pins numbered DQ0~DQ7. The TC59SM716AFT/AFTL configuration is  $4096 \times 512 \times 16$  of cell array with the DQ pins numbered DQ0~DQ15.

DataSheet4U.com www.DataSheet4U.com

### **ABSOLUTE MAXIMUM RATINGS**

| SYMBOL                             | PARAMETER                    | RATING                     | UNIT | NOTES |

|------------------------------------|------------------------------|----------------------------|------|-------|

| V <sub>IN</sub> , V <sub>OUT</sub> | Input, Output Voltage        | -0.3~V <sub>CC</sub> + 0.3 | V    | 1     |

| V <sub>CC</sub> , V <sub>CCQ</sub> | Power Supply Voltage         | -0.3~4.6                   | V    | 1     |

| T <sub>opr</sub>                   | Operating Temperature        | 0~70                       | °C   | 1     |

| T <sub>stg</sub>                   | Storage Temperature          | <b>−55~150</b>             | °C   | 1     |

| T <sub>solder</sub>                | Soldering Temperature (10s)  | 260                        | °C   | 1     |

| PD                                 | Power Dissipation            | 1                          | W    | 1     |

| lout                               | Short-Circuit Output Current | 50                         | mA   | 1     |

### RECOMMENDED DC OPERATING CONDITIONS (Ta = 0°~70°C)

| SYMBOL           | PARAMETER                            | MIN  | TYP. | MAX                   | UNIT | NOTES |

|------------------|--------------------------------------|------|------|-----------------------|------|-------|

| V <sub>CC</sub>  | Power Supply Voltage                 | 3    | 3.3  | 3.6                   | V    | 2     |

| V <sub>CCQ</sub> | Power Supply Voltage (for DQ Buffer) | 3    | 3.3  | 3.6                   | V    | 2     |

| VIH              | LVTTL Input High Voltage             | 2    | _    | V <sub>CC</sub> + 0.3 | V    | 2     |

| V <sub>IL</sub>  | LVTTL Input Low Voltage              | -0.3 | _    | 0.8                   | V    | 2     |

Note: V<sub>IH</sub> (max) = V<sub>CC</sub>/V<sub>CCQ</sub> + 1.2 V for pulse width  $\leq$  5 ns VIL (min) = V<sub>SS</sub>/V<sub>SSQ</sub> - 1.2 V for pulse width  $\leq$  5 ns

V<sub>CCQ</sub> must be less than or equal to V<sub>CC</sub>.

### et4U.com

### CAPACITANCE (V<sub>CC</sub> = 3.3 V, f = 1 MHz, Ta = 25 C) COM

| SYMBOL         | PARAMETER                                                                                                                                             | MIN | MAX | UNIT |

|----------------|-------------------------------------------------------------------------------------------------------------------------------------------------------|-----|-----|------|

| C <sub>I</sub> | Input Capacitance (A0~A11, BS0, BS1, $\overline{\text{CS}}$ , $\overline{\text{RAS}}$ , $\overline{\text{CAS}}$ , $\overline{\text{WE}}$ , DQM*, CKE) | _   | 4   | pF   |

|                | Input Capacitance (CLK)                                                                                                                               | _   | 5   | pF   |

| Co             | Input/Output Capacitance                                                                                                                              | _   | 6.5 | pF   |

Note: These parameters are periodically sampled and not 100% tested.

\* LDQM, UDQM (TC59SM716)

www.DataSheet4U.com

DataShe

### $\underline{\text{DC CHARACTERISTICS}} \; (\text{V}_{\text{CC}} = 3.3 \; \text{V} \pm 0.3 \; \text{V}, \; \text{Ta} = 0^{\circ} \text{~-} 70^{\circ} \text{C})$

| PARAMETER                                                                                                                                                                                  |                                            | SYMBOL             | -7     | 70  | -75 |     | -80 |     | UNITS | NOTES |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------|--------------------|--------|-----|-----|-----|-----|-----|-------|-------|

|                                                                                                                                                                                            |                                            | STIVIBUL           | MIN    | MAX | MIN | MAX | MIN | MAX | UNITS | NOTES |

| $\begin{aligned} & \text{OPERATING CURRENT} \\ & t_{CK} = \text{min, } t_{RC} = \text{min} \\ & \text{Active Precharge command cycling} \\ & \text{without burst operation} \end{aligned}$ | 1 bank operation                           | Icc1               |        | 80  |     | 75  |     | 70  |       | 3     |

| STANDBY CURRENT t <sub>CK</sub> = min, $\overline{CS} = V_{IH}$ ,                                                                                                                          | CKE = V <sub>IH</sub>                      | I <sub>CC2</sub>   |        | 40  |     | 35  |     | 30  |       | 3     |

| V <sub>IH/L</sub> = V <sub>IH</sub> (min) / V <sub>IL</sub> (max),<br>Bank: Inactive state                                                                                                 | CKE = V <sub>IL</sub><br>(Power Down mode) | I <sub>CC2P</sub>  |        | 1   |     | 1   |     | 1   |       | 3     |

| STANDBY CURRENT<br>CLK = V <sub>IL</sub> , CS = V <sub>IH</sub> ,                                                                                                                          | CKE = V <sub>IH</sub>                      | I <sub>CC2S</sub>  | _      | 10  | _   | 10  | _   | 10  |       |       |

| $V_{IH/L} = V_{IH}(min) / V_{IL}(max),$<br>Bank: Inactive state                                                                                                                            | CKE = V <sub>IL</sub><br>(Power Down mode) | I <sub>CC2PS</sub> | _      | 1   | _   | 1   | _   | 1   | mA.   |       |

| NO OPERATING CURRENT t <sub>CK</sub> = min, $\overline{CS} = V_{IH}(min)$ ,                                                                                                                | CKE = V <sub>IH</sub>                      | I <sub>CC3</sub>   |        | 60  |     | 55  |     | 50  | III/X |       |

| Bank: Active state (4 banks)                                                                                                                                                               | CKE = V <sub>IL</sub><br>(Power Down mode) | I <sub>CC3P</sub>  | _      | 10  | _   | 10  | -   | 10  |       |       |

| BURST OPERATING CURRENT t <sub>CK</sub> = min Read/Write command cycling                                                                                                                   |                                            | I <sub>CC4</sub>   | l      | 100 | l   | 95  | l   | 90  |       | 3, 4  |

| AUTO REFRESH CURRENT $t_{CK} = min, t_{RC} = min$ Auto Refresh command cycling                                                                                                             | Data                                       | I <sub>CC5</sub>   | _<br>- | 170 |     | 160 | -   | 150 |       | 3     |

| SELF REFRESH CURRENT Self Refresh mode                                                                                                                                                     | Standard Products<br>(AFT)                 | Joon               | _      | 2   | _   | 2   | _   | 2   |       |       |

| CKE = 0.2 V                                                                                                                                                                                | Low Power Version (AFTL)                   | I <sub>CC6</sub>   | _      | 800 | _   | 800 | _   | 800 | μА    |       |

et4U.com

DataShe

| PARAMETER                                                                                                       | SYMBOL             | MIN        | MAX | UNITS | NOTES |

|-----------------------------------------------------------------------------------------------------------------|--------------------|------------|-----|-------|-------|

| INPUT LEAKAGE CURRENT (0 V $\leq$ V <sub>IN</sub> $\leq$ V <sub>CC</sub> , all other pins not under test = 0 V) | I <sub>I</sub> (L) | <b>-</b> 5 | 5   | μА    |       |

| OUTPUT LEAKAGE CURRENT (Output disable, 0 V $\leq$ V <sub>OUT</sub> $\leq$ V <sub>CCQ</sub> )                   | I <sub>O</sub> (L) | <b>-</b> 5 | 5   | μА    |       |

| LVTTL OUTPUT H LEVEL VOLTAGE (I <sub>OUT</sub> = -2 mA)                                                         | V <sub>OH</sub>    | 2.4        | _   | V     |       |

| LVTTL OUTPUT L LEVEL VOLTAGE (I <sub>OUT</sub> = 2 mA)                                                          | V <sub>OL</sub>    | _          | 0.4 | V     |       |

### **AC CHARACTERISTICS AND OPERATING CONDITIONS**

$(V_{CC} = 3.3 \text{ V} \pm 0.3 \text{ V}, \text{ Ta} = 0^{\circ} \sim 70^{\circ}\text{C}) \text{ (Notes: 5, 6, 7)}$

|                  | L PARAMETER -                          |            | -70 |         | -75 |        | -80 |        |       | NOTEO |

|------------------|----------------------------------------|------------|-----|---------|-----|--------|-----|--------|-------|-------|

| SYMBOL           |                                        |            | MIN | MAX     | MIN | MAX    | MIN | MAX    | UNITS | NOTES |

| t <sub>RC</sub>  | Ref/Active to Ref/Active Command F     | Period     | 57  | _       | 65  | _      | 68  | _      |       |       |

| t <sub>RAS</sub> | Active to Precharge Command Period     |            | 42  | 100000  | 45  | 100000 | 48  | 100000 | ns    |       |

| t <sub>RCD</sub> | Active to Read/Write Command Dela      | ay Time    | 15  | _       | 20  | _      | 20  | _      |       | 9     |

| tccd             | Read/Write(a) to Read/Write(b) Comm    | and Period | 1   | _       | 1   | _      | 1   | _      | Cycle | 9     |

| t <sub>RP</sub>  | Precharge to Active Command Period     | od         | 15  | _       | 20  | _      | 20  | _      |       |       |

| t <sub>RRD</sub> | Active(a) to Active(b) Command Per     | iod        | 15  | _       | 15  | _      | 20  | _      |       |       |

| 4                | W. ''. D. T'                           | CL* = 2    | 7.5 | _       | 10  | _      | 10  | _      |       |       |

| t <sub>WR</sub>  | Write-Recovery Time                    | CL* = 3    | 7   | _       | 7.5 | _      | 8   | _      |       |       |

| 4                | CLK Cycle Time                         | CL* = 2    | 7.5 | 1000    | 10  | 1000   | 10  | 1000   |       |       |

| t <sub>CK</sub>  | CLK Cycle Time                         | CL* = 3    | 7   | 1000    | 7.5 | 1000   | 8   | 1000   |       |       |

| t <sub>CH</sub>  | CLK High-Level Width                   |            | 2.5 | _       | 2.5 | _      | 3   | _      |       | 10    |

| t <sub>CL</sub>  | CLK Low-Level Width                    |            | 2.5 | _       | 2.5 | _      | 3   | _      |       | 10    |

| 4                | T                                      | CL* = 2    | _   | 5.4     | _   | 6      | _   | 6      |       |       |

| t <sub>AC</sub>  | Access Time from CLK                   | CL* = 3    | _   | 5.4     | _   | 5.4    | _   | 6      |       |       |

| tон              | Output Data Hold Time                  |            | 3   | _       | 3   | _      | 3   | _      |       |       |

| t <sub>HZ</sub>  | Output Data High-Impedance Time        | DetaS      | 3   | 7       | 3   | 7.5    | 3   | 8      | ns    | 8     |

| $t_{LZ}$         | Output Data Low-Impedance Time         | Datas      | 0   | U.COIII | 0   | _      | 0   | _      |       |       |

| t <sub>SB</sub>  | Power-Down Mode Entry Time             |            | 0   | 7       | 0   | 7.5    | 0   | 8      |       |       |

| tt               | Transition Time of CLK (rise and fall) | )          | 0.5 | 10      | 0.5 | 10     | 0.5 | 10     |       |       |

| t <sub>DS</sub>  | Data-In Set-up Time                    |            | 1.5 | _       | 1.5 | _      | 2   | _      |       |       |

| t <sub>DH</sub>  | Data-In Hold Time                      |            | 0.8 |         | 0.8 |        | 1   |        |       |       |

| tas              | Address Set-up Time                    |            | 1.5 | _       | 1.5 | _      | 2   |        |       |       |

| t <sub>AH</sub>  | Address Hold Time                      |            | 0.8 |         | 0.8 |        | 1   |        |       |       |

| t <sub>CKS</sub> | CKE Set-up Time                        |            | 1.5 |         | 1.5 |        | 2   |        |       |       |

| t <sub>CKH</sub> | CKE Hold Time                          |            | 0.8 | _       | 0.8 |        | 1   |        |       |       |

| t <sub>CMS</sub> | Command Set-up Time                    |            | 1.5 |         | 1.5 |        | 2   |        |       |       |

| tcmH             | Command Hold Time                      |            | 0.8 |         | 0.8 |        | 1   |        |       |       |

| t <sub>REF</sub> | Refresh Time                           |            | _   | 64      |     | 64     |     | 64     | ms    |       |

| t <sub>RSC</sub> | Mode Register Set Cycle Time           |            | 14  | _       | 15  | _      | 16  | _      | ns    | 9     |

<sup>\*</sup> CL means CAS latency.

DataShe

DataSheet4U.com www.DataSheet4U.com

#### NOTES:

- (1) Conditions outside the limits listed under "ABSOLUTE MAXIMUM RATINGS" may cause permanent damage to the device.

- (2) All voltages are referenced to VSS.

- (3) These parameters depend on the cycle rate and these values are measured at a cycle rate with the minimum values of tCK and tRC. Input signals are changed one time during tCK.

- (4) These parameters depend on the output loading. Specified values are obtained with the output open.

- (5) Power-up sequence is described in Note 11.

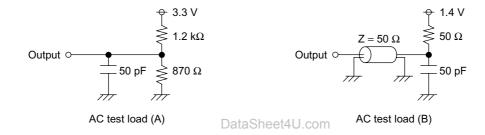

- (6) AC TEST CONDITIONS

| Output Reference Level                           | 1.4 V, 1.4 V        |

|--------------------------------------------------|---------------------|

| Output Load                                      | See diagram B below |

| Input Signal Levels                              | 2.4 V, 0.4 V        |

| Transition Time (rise and fall) of Input Signals | 2 ns                |

| Input Reference Level                            | 1.4 V               |

et4U.com

DataShe

- (7) Transition times are measured between  $V_{\rm IH}$  and  $V_{\rm IL}$ . Transition (rise and fall) of input signals have a fixed slope.

- (8) tHZ defines the time at which the outputs achieve the open circuit condition and is not referenced to output voltage levels.

www.DataSheet4U.com

- (9) These parameters account for the number of clock cycles and depend on the operating frequency of the clock, as follows:

- the number of clock cycles = specified value of timing / clock period (count fractions as a whole number)

- (10) tCH is the pulse width of CLK measured from the positive edge to the negative edge referenced to VIH (min). tCL is the pulse width of CLK measured from the negative edge to the positive edge referenced to VIL (max).

- (11) Power-up Sequence

Power-up must be performed in the following sequence.

- 1) Power must be applied to  $V_{CCQ}$  (simultaneously) while all input signals are held in the "NOP" state. The CLK signals must be started at the same time.

- 2) After power-up a pause of at least 200  $\mu s$  is required. It is required that DQM and CKE signals must be held "High" (VCC levels) to ensure that the DQ output is in High-impedance state.

- 3) All banks must be precharged.

- 4) The Mode Register Set command must be asserted to initialize the Mode Register.

- 5) A minimum of eight Auto Refresh dummy cycles is required to stabilize the internal circuitry of the device.

The Mode Register Set command can be invoked either before or after the Auto Refresh dummy cycles.

### (12) AC Latency Characteristics

| CKE to clock disable (CKE Latency)                     | 1      |                      |             |

|--------------------------------------------------------|--------|----------------------|-------------|

| DQM to output in High-Z (Read DQM Latency)             | 2      |                      |             |

| DQM to input data delay (Write DQM Latency)            |        | 0                    |             |

| Write command to input data (Write Data Latency)       |        | 0                    |             |

| CS to Command input (CS Latency)                       |        | 0                    |             |

| Prophers to DO Hi 7 Load time                          | CL = 2 | 2                    |             |

| Precharge to DQ Hi-Z Lead time                         | CL = 3 | 3                    | Cycle       |

| Precharge to Last Valid data out                       |        | 1                    |             |

|                                                        |        | 2                    |             |

| Burst Stan Command to DO Hi 71 and time                | CL = 2 | 2                    |             |

| Burst Stop Command to DQ Hi-Z Lead time                | CL = 3 | 3                    |             |

| Duret Stan Command to Leat Valid data out              | CL = 2 | 1                    |             |

| Burst Stop Command to Last Valid data out              |        | 2                    |             |

| Read with Autoprecharge Command to Active/Ref Command  |        | BL + t <sub>RP</sub> |             |

|                                                        |        | BL + t <sub>RP</sub> | Cycle + ns  |

| Write with Autoprecharge Command to Active/Ref Command |        | BL + t <sub>RP</sub> | Cycle + IIS |

|                                                        |        | BL + t <sub>RP</sub> |             |

et4U.com

DataShe

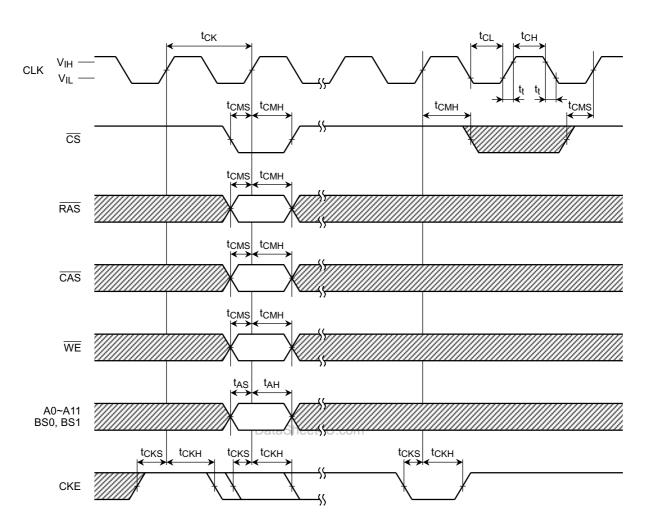

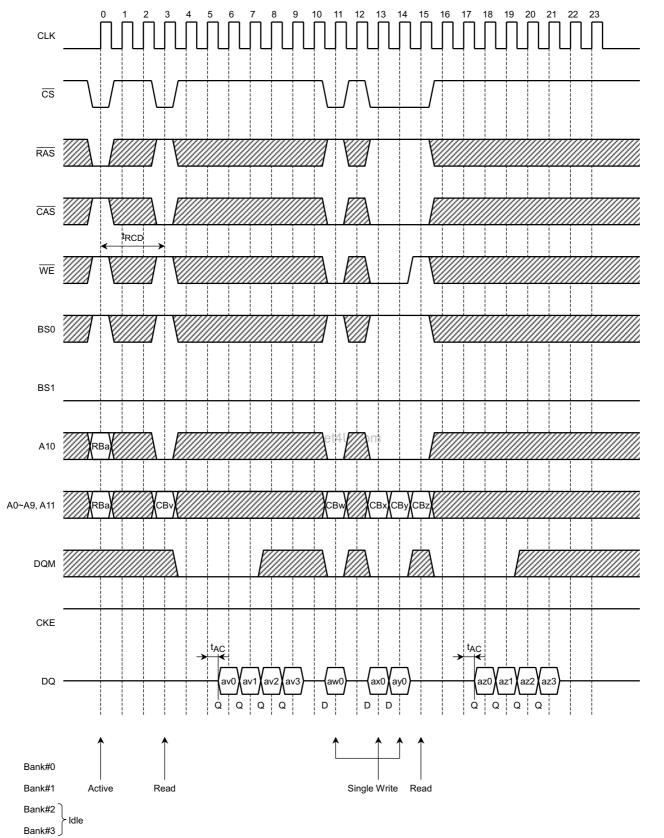

### **TIMING DIAGRAMS**

### **Command Input Timing**

et4U.com

DataShe

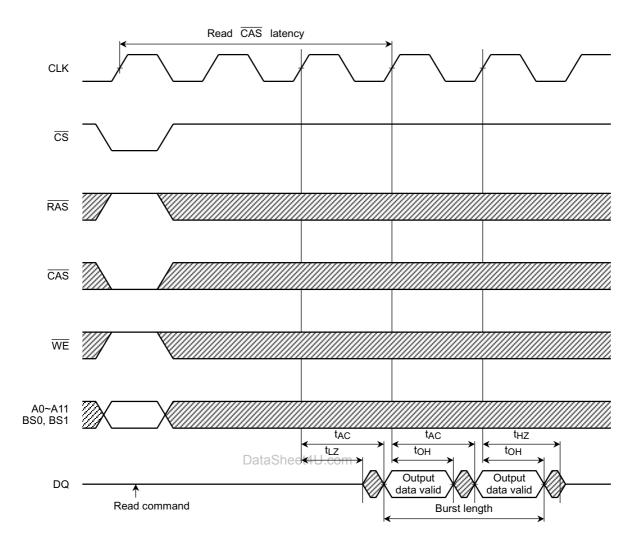

### **Read Timing**

et4U.com

DataShe

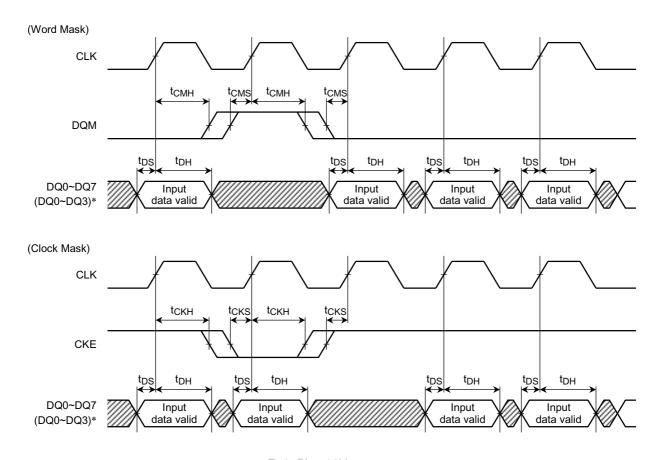

#### Control Timing of Input Data (TC59SM708/M704)

et4U.com

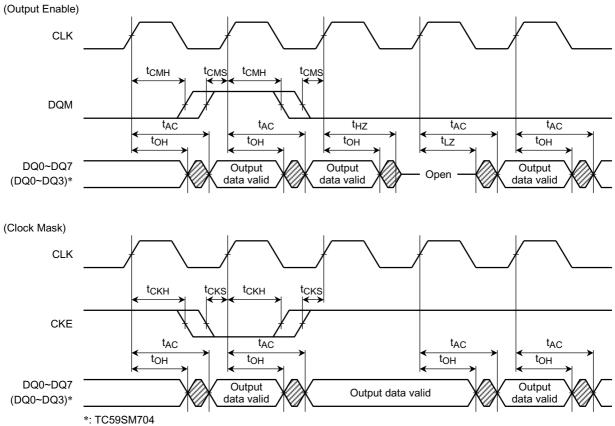

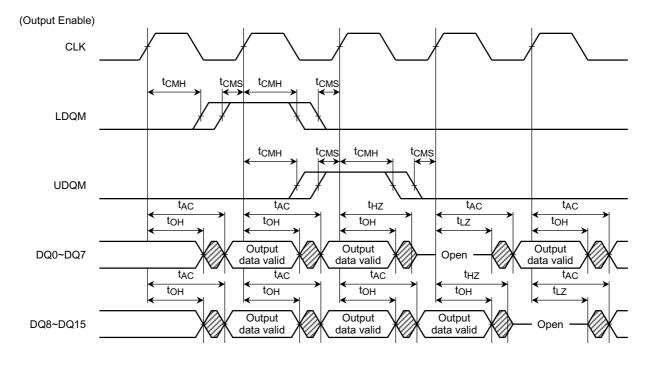

### Control Timing of Output Data (TC59SM708/M704)

DataShe

DataSheet4U.com

www.DataSheet4U.com

2000-02-08 11/49

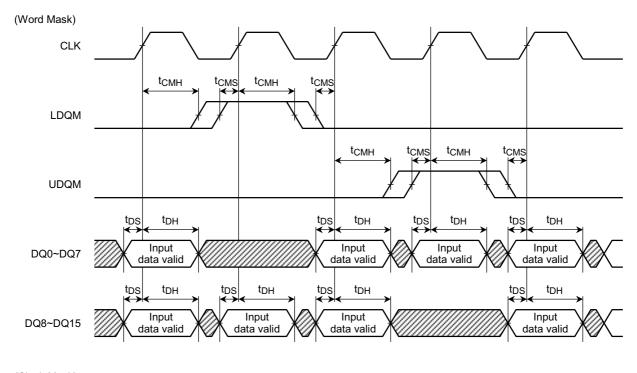

### Control Timing of Input Data (TC59SM716)

et4U.com

DataShe

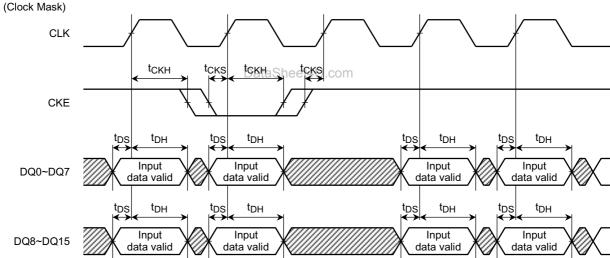

### Control Timing of Output Data (TC59SM716)

et4U.com

DataShe

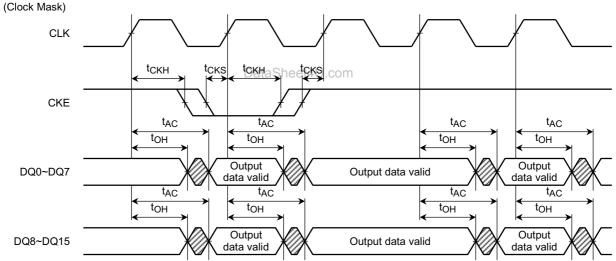

### Mode Register Set Cycle

DataSheet4U.com www.DataSheet4U.com

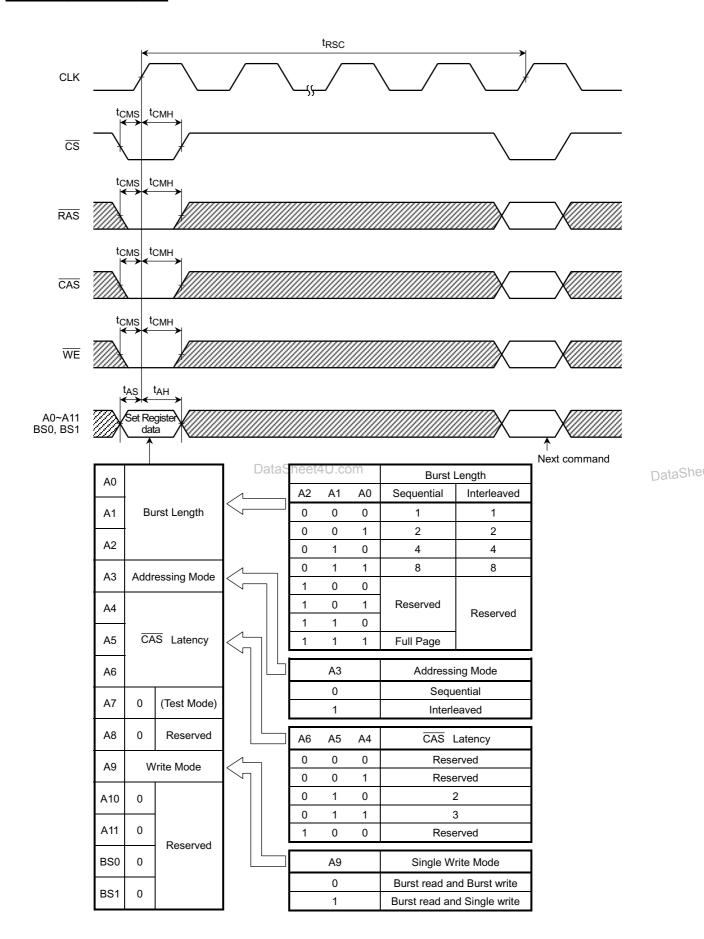

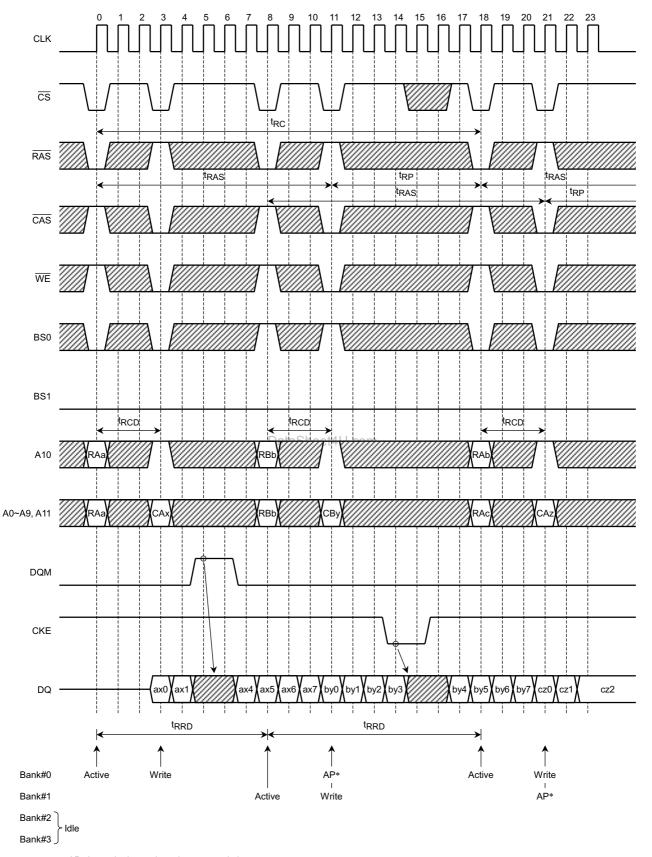

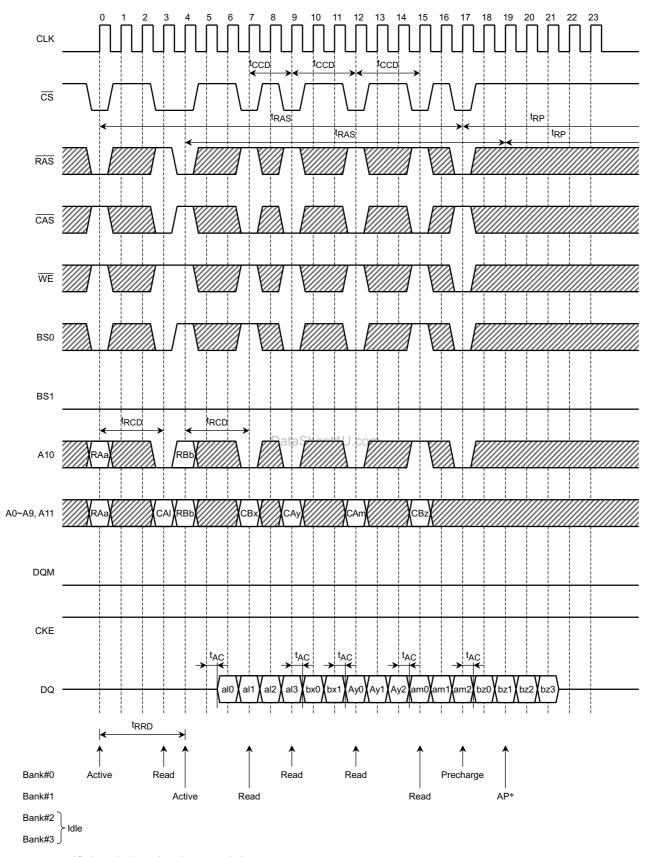

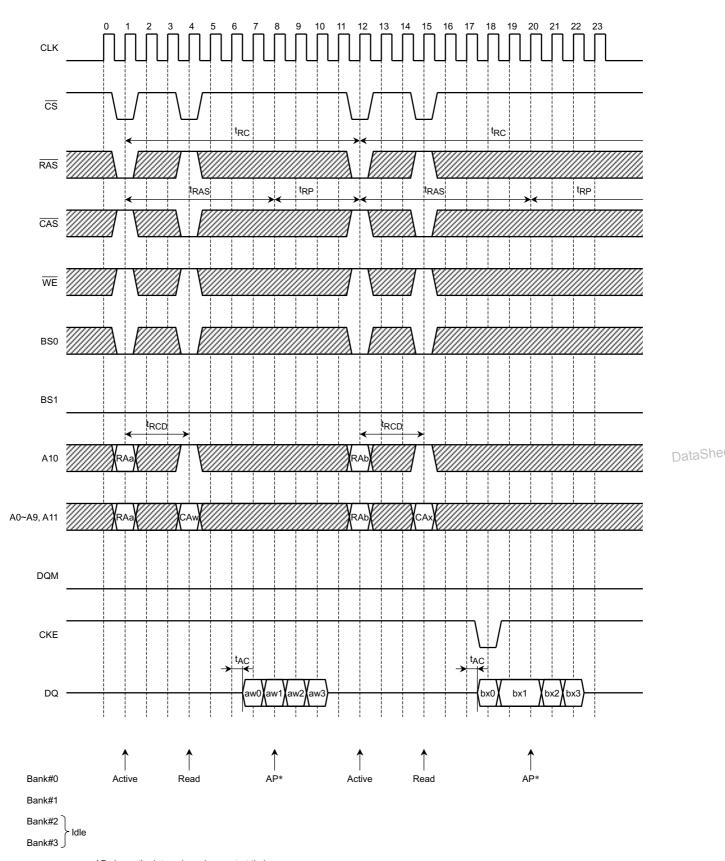

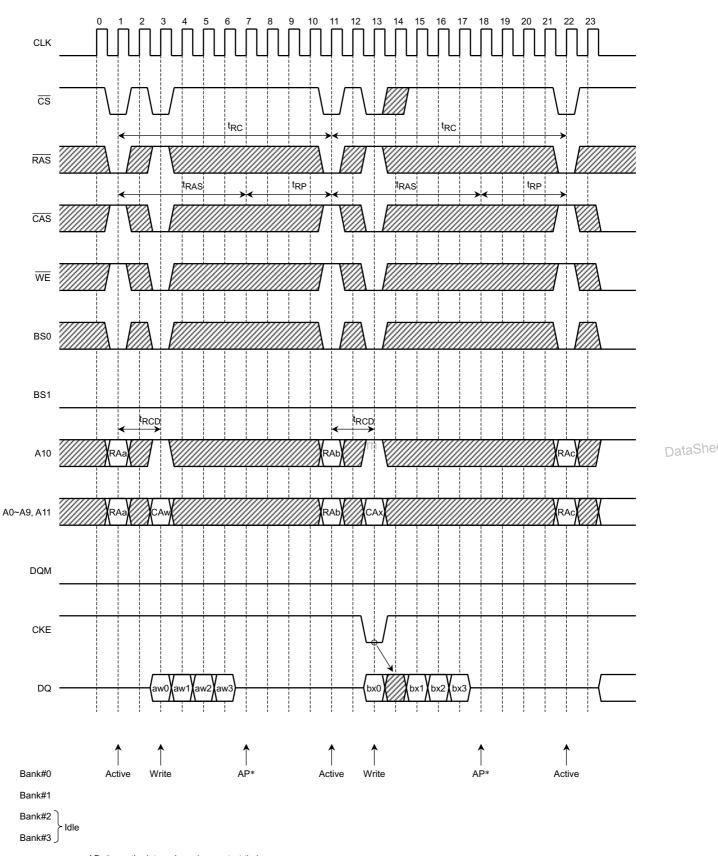

### **OPERATING TIMING EXAMPLE**

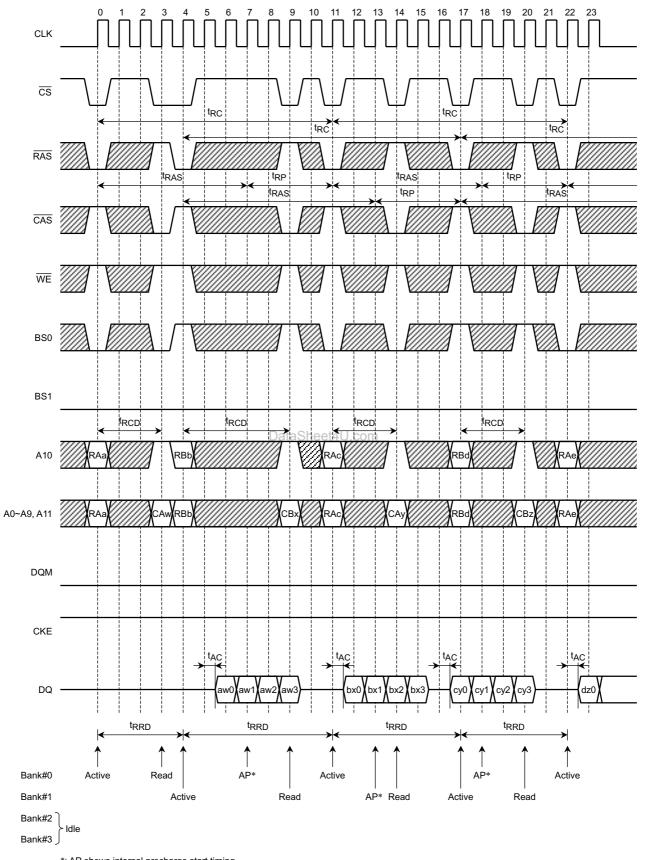

Figure 1. Interleaved Bank Read (Burst Length = 4, CAS Latency = 3)

et4U.com

www.DataSheet4U.com

2000-02-08 15/49

Figure 2. Interleaved Bank Read (Burst Length = 4, CAS Latency = 3, Auto Precharge)

<sup>\*:</sup> AP shows internal precharge start timing.

www.DataSheet4U.com

DataShe

2000-02-08 16/49

et4U.com

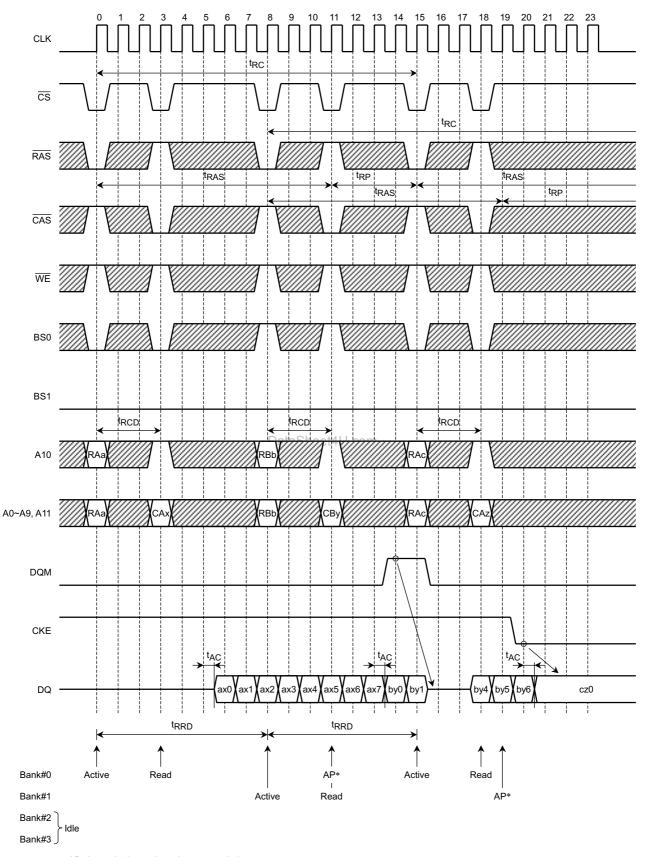

Figure 3. Interleaved Bank Read (Burst Length = 8, CAS Latency = 3)

et4U.com

www.DataSheet4U.com

Figure 4. Interleaved Bank Read (Burst Length = 8, CAS Latency = 3, Auto Precharge)

$\ast \! : \! \mathsf{AP}$  shows the internal precharge start timing.

DataSheet4U.com www.DataSheet4U.com

2000-02-08 18/49

DataShe

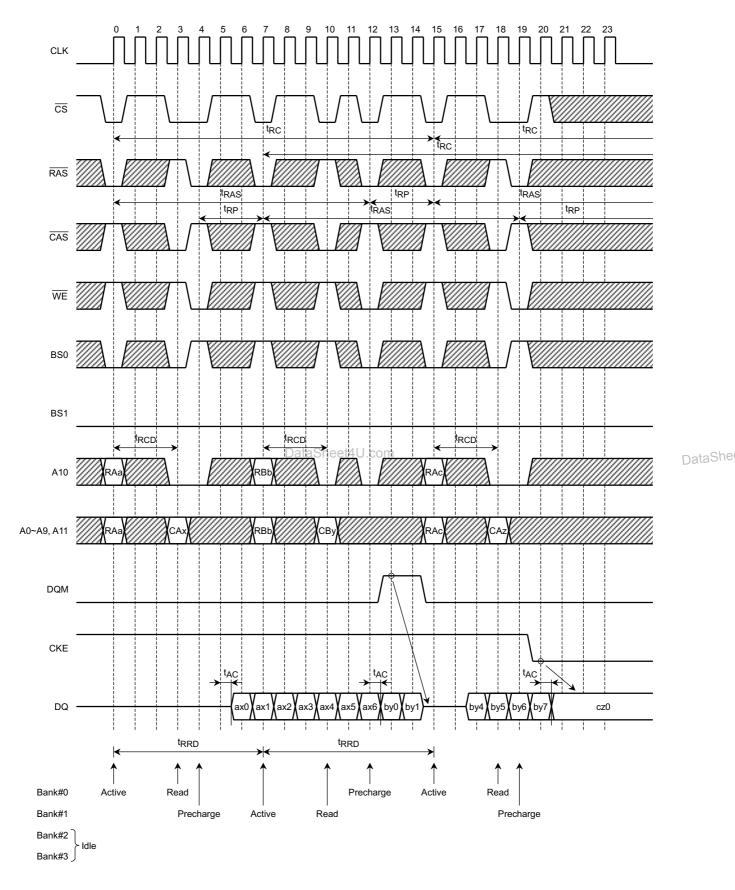

Figure 5. Interleaved Bank Write (Burst Length = 8)

DataSheet4U.com www.DataSheet4U.com

2000-02-08 19/49

Figure 6. Interleaved Bank Write (Burst Length = 8, Auto Precharge)

$\ast \! : \! \mathsf{AP}$  shows the internal precharge start timing.

DataSheet4U.com www.DataSheet4U.com

2000-02-08 20/49

DataShe

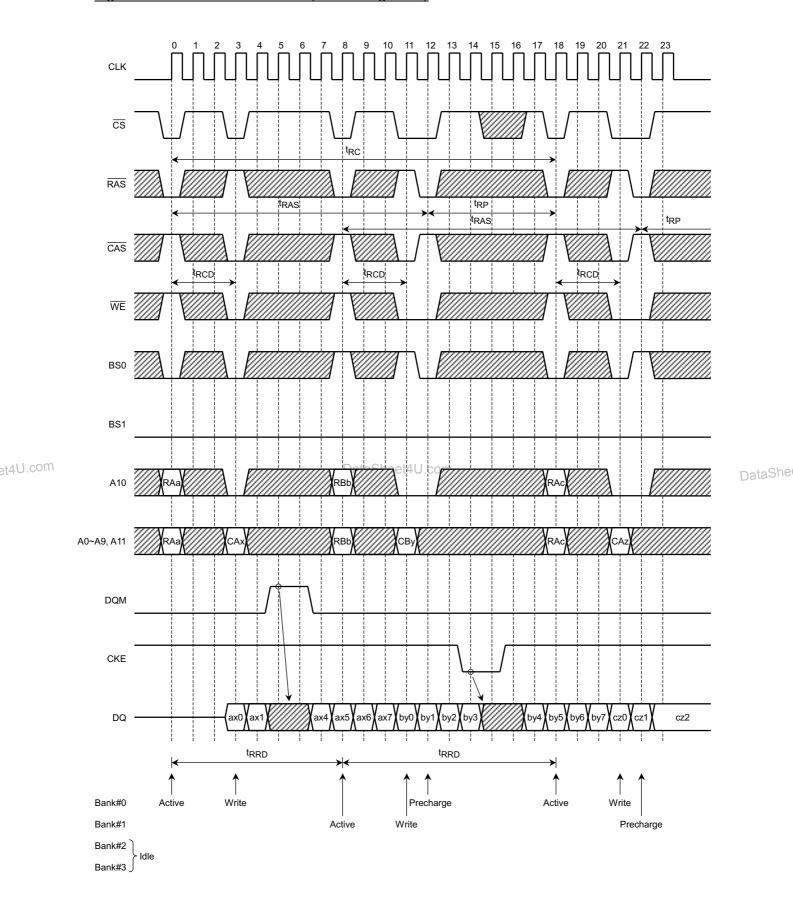

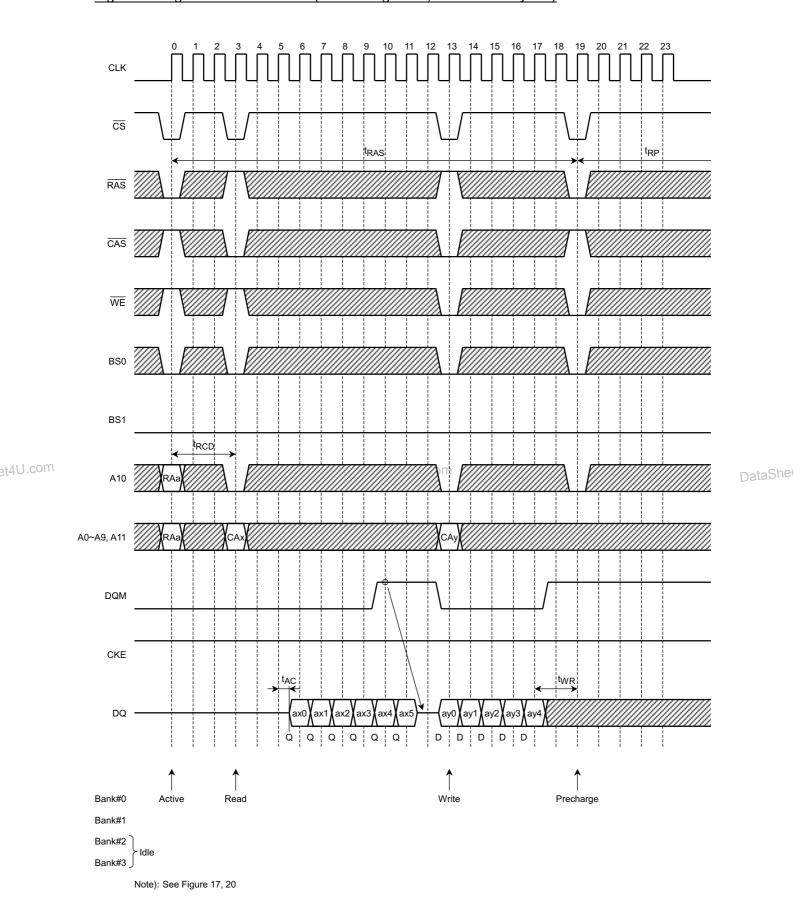

Figure 7. Page Mode Read (Burst Length = 4, CAS Latency = 3)

$\ast \text{:}\ \mathsf{AP}\ \mathsf{shows}\ \mathsf{the}\ \mathsf{internal}\ \mathsf{precharge}\ \mathsf{start}\ \mathsf{timing}.$

DataSheet4U.com www.DataSheet4U.com

2000-02-08 21/49

DataShe

Figure 8. Page Mode Read/Write (Burst Length = 8, CAS Latency = 3)

DataSheet4U.com www.DataSheet4U.com

2000-02-08 22/49

Figure 9. Auto Precharge Read (Burst Length = 4, CAS Latency = 3)

e: AP shows the internal precharge start timing.

Note): See Figure 15

DataSheet4U.com www.DataSheet4U.com

Figure 10. Auto Precharge Write (Burst Length = 4)

\*: AP shows the internal precharge start timing.

Note): See Figure 16

DataSheet4U.com www.DataSheet4U.com

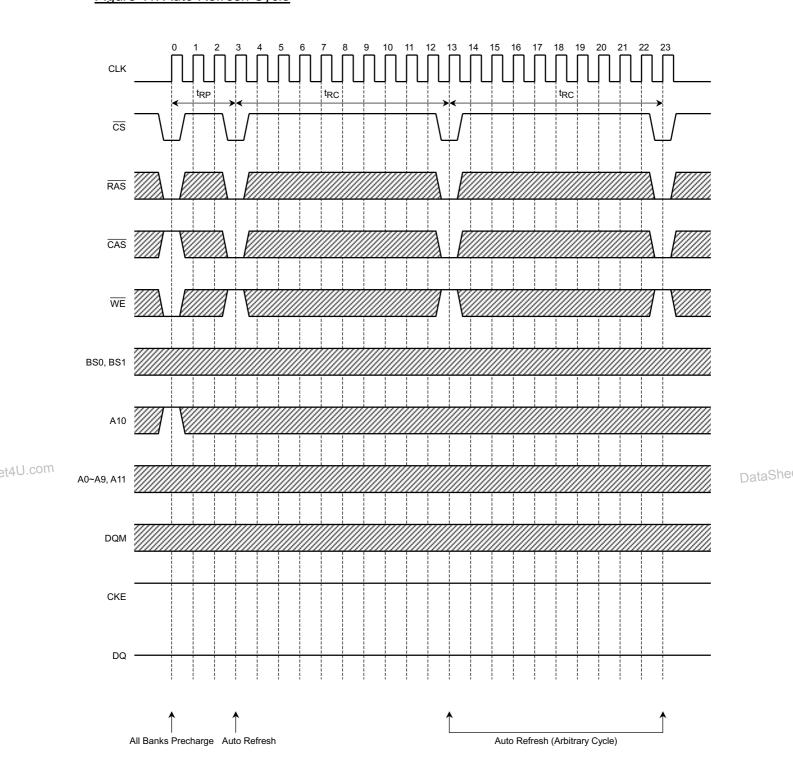

### Figure 11. Auto Refresh Cycle

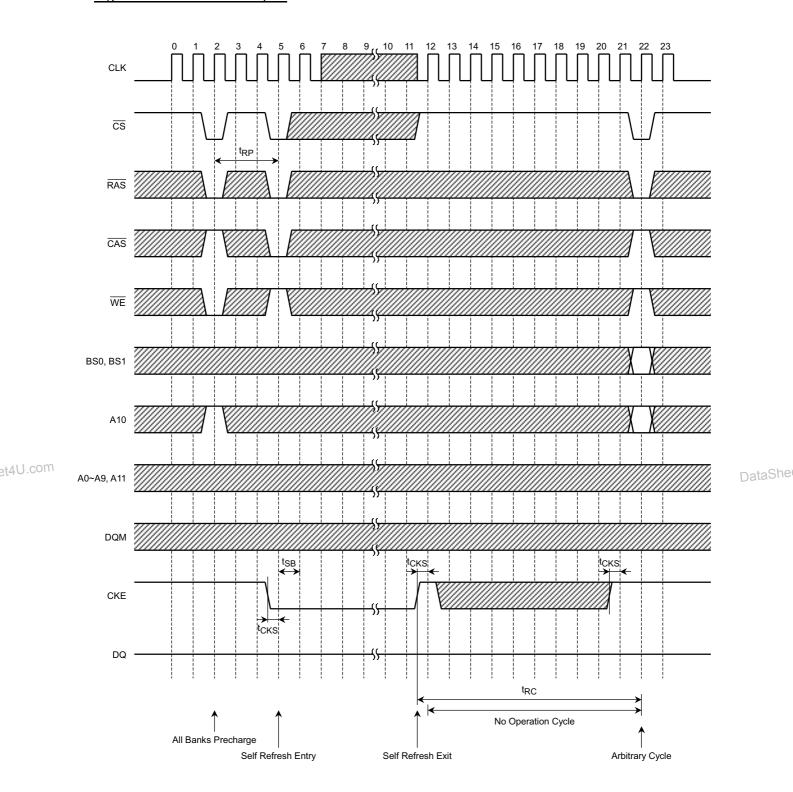

Figure 12. Self Refresh Cycle

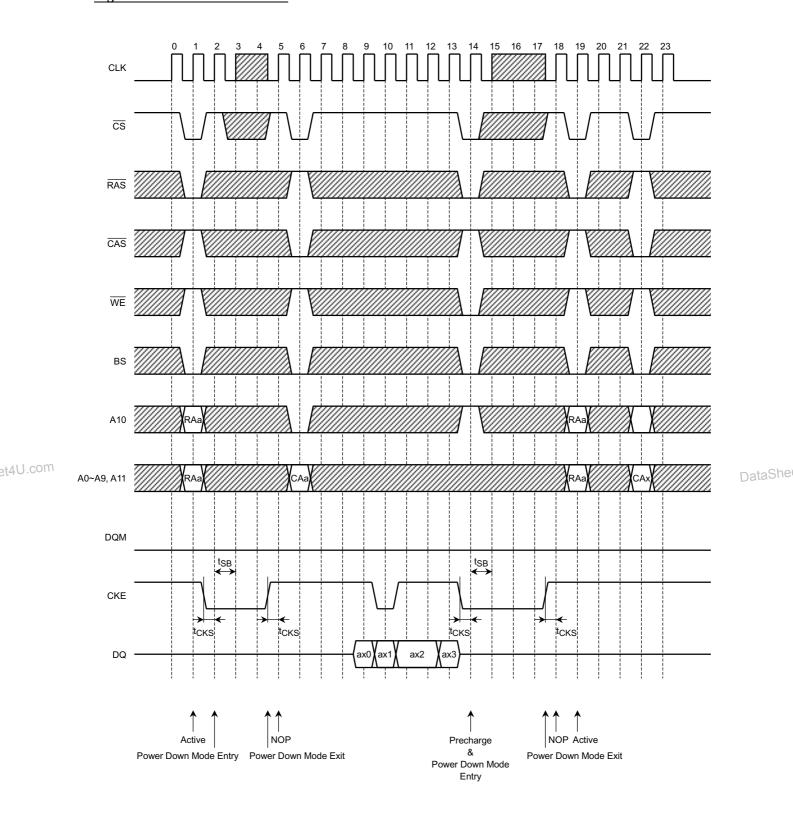

Figure 13. Power Down Mode

Note): The Power Down mode is invoked by asserting CKE "low".

$\label{limit} \mbox{All Input/Output buffers (except the CKE buffer) are turned off in Power Down mode.}$

When CKE goes high, the No-operation command input must be at next CLK rising edge.

Figure 14. Burst Read and Single Write (Burst Length = 4, CAS Latency = 3)

et4U.com

DataShe

### **PIN FUNCTIONS**

#### **CLOCK INPUT: CLK**

The CLK input is used as the reference for SDRAM operations. Operations are synchronized to the positive edges of CLK.

#### **CLOCK ENABLE: CKE**

The CKE input is used to suspend the internal CLK. When the CKE signal is asserted "low", the internal CLK is suspended and output data is held intact while CKE is asserted "low". When the device is not running a Burst cycle, the CKE input controls the entry to the Power Down and Self Refresh modes. When the Self Refresh command is issued, the device must be in the idle state.

#### BANK SELECT: BS0, BS1

The TC59SM716AFT/AFTL, TC59SM708AFT/AFTL and the TC59SM704AFT/AFTL are organized as four-bank memory cell arrays. The BS0, BS1 inputs are latched at the time of assertion of the operation commands and selects the bank to be used for the operation.

| BS0 | BS1 |        |

|-----|-----|--------|

| 0   | 0   | Bank#0 |

| 1   | 0   | Bank#1 |

| 0   | 1   | Bank#2 |

| 1   | 1   | Bank#3 |

#### ADDRESS INPUTS: A0~A11

The A0~A11 inputs are address to access the memory cell array, as following table.

|                   | Row Address | Column Address |

|-------------------|-------------|----------------|

| TC59SM716AFT/AFTL | A0~A11      | A0~A8          |

| TC59SM708AFT/AFTL | A0~A11      | A0~A9          |

| TC59SM704AFT/AFTL | A0~A11      | A0~A9, A11     |

The row address bits are latched at the Bank Activate command and column address bits are latched on the Read or Write command. Also, the  $A0\sim A11$  inputs are used to set the data in the Mode register in a Mode Register Set cycle.

DataShe

DataSheet4U.com www.DataSheet4U.com

### CHIP SELECT: CS

The  $\overline{CS}$  input controls the latching of the commands on the positive edges of CLK when  $\overline{CS}$  is asserted "low". No commands are latched as long as  $\overline{CS}$  is held "high".

### ROW ADDRESS STROBE: RAS

The  $\overline{RAS}$  input defines the operation commands in conjunction with the  $\overline{CAS}$  and  $\overline{WE}$  inputs, and is latched at the positive edges of CLK. When  $\overline{RAS}$  and  $\overline{CS}$  are asserted "low" and  $\overline{CAS}$  is asserted "high", either the Bank Activate command or the Precharge command is selected by the  $\overline{WE}$  signal. When  $\overline{WE}$  is asserted "high", the Bank Activate command is selected and the bank designated by BS0, BS1 are turned on so that it is in the active state. When  $\overline{WE}$  is asserted "low", the Precharge command is selected and the bank designated by BS0, BS1 are switched to the idle state after Precharge operation.

### **COLUMN ADDRESS STROBE: CAS**

The  $\overline{\text{CAS}}$  input defines the operation commands in conjunction with the  $\overline{\text{RAS}}$  and  $\overline{\text{WE}}$  inputs, and is latched at the positive edges of CLK. When  $\overline{\text{RAS}}$  is held "high" and  $\overline{\text{CS}}$  is asserted "low", column access is started by asserting  $\overline{\text{CAS}}$  "low". Then, the Read or Write command is selected by asserting  $\overline{\text{WE}}$  "low" or "high".

#### WRITE ENABLE: WE

The  $\overline{WE}$  input defines the operation commands in conjunction with the  $\overline{RAS}$  and  $\overline{CAS}$  inputs, and is latched at the positive edges of CLK. The  $\overline{WE}$  input is used to select the Bank Activate or Precharge command and Read or Write command.

### DATA INPUT/OUTPUT MASK: DQM or L-DQM and U-DQM

The DQM input enables output in a Read cycle and functions as the input data mask in a Write cycle. When DQM is asserted "high" at the positive edges of CLK, output data is disabled after two clock cycles during a Read cycle, and input data is masked at the same clock cycle during a Write cycle.

In the case of the TC59SM716AFT/AFTL, the LDQM and UDQM inputs function as byte data control. The LDQM input can control DQ0~DQ7 in a Read or Write cycle and the UDQM can control DQ8~DQ15 in a Read or Write cycle.

DataShe

#### DATA INPUT/OUTPUT: DQ0~DQ15

The DQ0~DQ15 input and output data are synchronized with the positive edges of CLK. In the case of TC59SM708AFT/AFTL and TC59SM704AFT/AFTL, these pins are DQ0~DQ7 and DQ0~DQ3 respectively.

ptaSheet4U.com www.DataSheet4U.com

### **Operation Mode**

Table 1 shows the truth table for the operation commands.

Table 1. Truth Table (Note (1) and (2))

| Table 1. Truth Table (Note (1) and (2)) |                        |                    |                  |                    |             |     |               |        |     |        |    |

|-----------------------------------------|------------------------|--------------------|------------------|--------------------|-------------|-----|---------------|--------|-----|--------|----|

| Command                                 | Device State           | CKE <sub>n-1</sub> | CKE <sub>n</sub> | DQM <sup>(5)</sup> | BS0,<br>BS1 | A10 | A11,<br>A9~A0 | CS     | RAS | CAS    | WE |

| Bank Activate                           | Idle (3)               | Н                  | Х                | Х                  | V           | V   | V             | L      | L   | Н      | Н  |

| Bank Precharge                          | Any                    | Н                  | Х                | Х                  | V           | L   | Х             | L      | L   | Н      | L  |

| Precharge All                           | Any                    | Н                  | Х                | Х                  | Х           | Н   | Х             | L      | L   | Н      | L  |

| Write                                   | Active (3)             | Н                  | Х                | Х                  | >           | L   | V             | Ш      | Н   | L      | L  |

| Write with Auto Precharge               | Active (3)             | Н                  | Х                | Х                  | ٧           | Н   | V             | L      | Н   | L      | L  |

| Read                                    | Active (3)             | Н                  | Х                | Х                  | ٧           | L   | V             | L      | Н   | L      | Н  |

| Read with Auto Precharge                | Active (3)             | Н                  | Х                | Х                  | V           | Н   | V             | L      | Н   | L      | Н  |

| Mode Register Set                       | Idle                   | Н                  | Х                | Х                  | V           | V   | V             | L      | L   | L      | L  |

| No-Operation                            | Any                    | Н                  | Х                | Х                  | Х           | Х   | Х             | L      | Н   | Н      | Н  |

| Burst stop                              | Active (4)             | Н                  | Х                | Х                  | Х           | Х   | Х             | L      | Н   | Н      | L  |

| Device Deselect                         | Any                    | Н                  | Х                | Х                  | Х           | Х   | Х             | Н      | Х   | Х      | Х  |

| Auto-Refresh                            | Idle                   | Н                  | Н                | Х                  | Х           | Х   | Х             | L      | L   | L      | Н  |

| Self-Refresh Entry                      | Idle                   | Н                  | L                | Х                  | Х           | Х   | Х             | L      | L   | L      | Н  |

| Self-Refresh Exit                       | Idle<br>(Self Refresh) | L                  | Н                | Х                  | x           | х   | х             | Н .    | Х   | Х      | Х  |

|                                         |                        | Da                 | taShe            | et41 <b>k</b> .cor | n v         |     |               | L      | Н   | Н      | X  |

| Clock Suspend Mode Entry                | Active                 | НЪ                 | ιαφπο            | <b>X</b> .001      | ПХ          | Х   | Х             | X      | X   | X      | X  |

| Power Down Mode Entry                   | Idle/Active (6)        | Н                  | L                | Х                  | Х           | Х   | Х             | Н      | Х   | Х      | Х  |

|                                         |                        |                    |                  |                    |             |     |               | L      | Н   | Н      | Х  |

| Clock Suspend Mode Exit                 | Active                 | L                  | Н                | Х                  | Х           | Х   | Х             | Х      | Х   | Х      | Х  |

| Power Down Mode Exit                    | Any<br>(Power Down)    | L                  | Н                | ×                  | Х           | Х   | х             | H<br>L | Х   | X<br>H | X  |

| Data Write/Output Enable                | Active                 | Н                  | Х                | L                  | X           | Х   | Х             | X      | X   | X      | Х  |

| Data Write/Output Disable               | Active                 | Н                  | Х                | Н                  | Х           | Х   | Х             | Х      | Х   | Х      | Х  |

| ·                                       | 1                      | l                  | l                |                    |             | l   |               |        | [   | I      | l  |

et4U.com

- Note 1. V = Valid, X = Don't Care, L = Low level, H = High level

- CKE<sub>n</sub> signal is input level when commands are issued.

CKE<sub>n-1</sub> signal is input level one clock cycle before the commands are issued.

- 3. These are state designated by the BS0, BS1 signals.

- 4. Device state is Full Page Burst operation.

- 5. LDQM, UDQM (TC59SM716AFT/AFTL)

- Power Down Mode can not entry in the burst cycle.

When this command assert in the burst cycle, device state is clock suspend mode.

DataShe

2000-02-08 31/49

DataSheet4U.com

www.DataSheet4U.com

### 1. Command Function

#### 1-1 Bank Activate command

$$(\overline{RAS} = L, \overline{CAS} = H, \overline{WE} = H, BS = Bank, A0~A11 = Row Address)$$

The Bank Activate command activates the bank designated by the BS (Bank Select) signal.

Row addresses are latched on A0~A11 when this command is issued and the cell data is read out to the sense amplifiers. The maximum time that each bank can be held in the active state is specified as tRAS (max).

#### 1-2 Bank Precharge command

$$(\overline{RAS} = L, \overline{CAS} = H, \overline{WE} = L, BS = Bank, A10 = L, A0\sim A9, A11 = Don't care)$$

The Bank Precharge command precharges the bank designated by BS. The precharged bank is switched from the active state to the idle state.

#### 1-3 Precharge All command

$$(\overline{RAS} = L, \overline{CAS} = H, \overline{WE} = L, BS = Don't care, A10 = H, A0~A9, A11 = Don't care)$$

The Precharge All command precharges all banks simultaneously. All banks are then switched to the idle state.

#### 1-4 Write command

$$(\overline{RAS} = H, \overline{CAS} = L, \overline{WE} = L, BS = Bank, A10 = L, A0 \sim A9, A11 = Column Address)$$

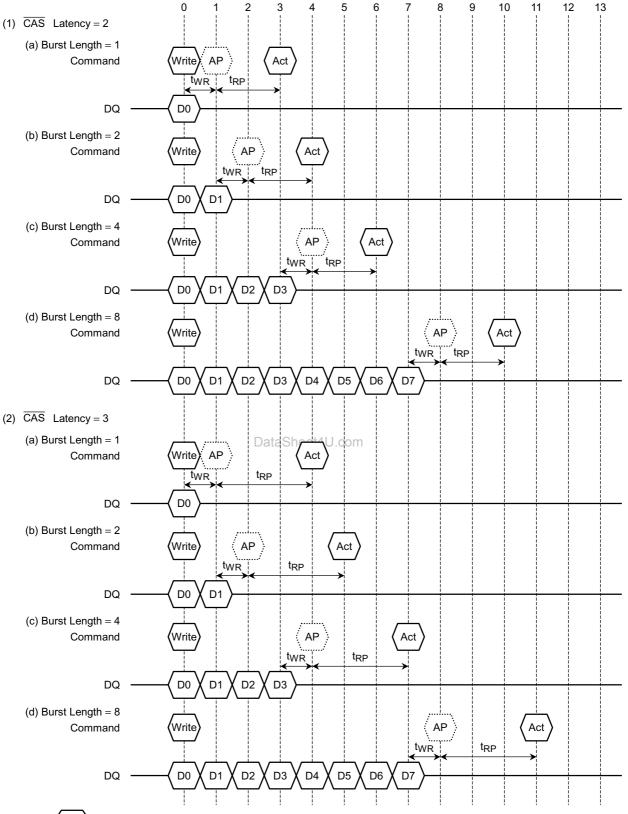

The Write command performs a Write operation to the bank designated by BS. The write data is latched at the positive edges of CLK. The length of the write data (Burst Length) and column access sequence (Addressing Mode) must be programmed in the Mode Resister at power-up prior to the Write operation.

The A11 input is "Don't care" on the TC59SM708AFT/AFTL and the A9 and A11 inputs are "Don't care" on the TC59SM716AFT/AFTL.

### 1-5 Write with Auto Precharge command DataSheet4U.com

```

(\overline{RAS} = H, \overline{CAS} = L, \overline{WE} = L, BS = Bank, A10 = H, A0 \sim A9, A11 = Column Address)

```

The Write with Auto Precharge command performs the Precharge operation automatically after the Write operation. The internal precharge starts in the cycles immediately following the cycle in which the last data is written independent of  $\overline{CAS}$  Latency (Figure 16). This command must not be interrupted by any other commands.

The A11 input is "Don't care" at the TC59SM708AFT/AFTL and the A9 and A11 inputs are "Don't care" on the TC59SM716AFT/AFTL.

#### 1-6 Read command

$$(\overline{RAS} = H, \overline{CAS} = L, \overline{WE} = H, BS = Bank, A10 = L, A0 \sim A9, A11 = Column Address)$$

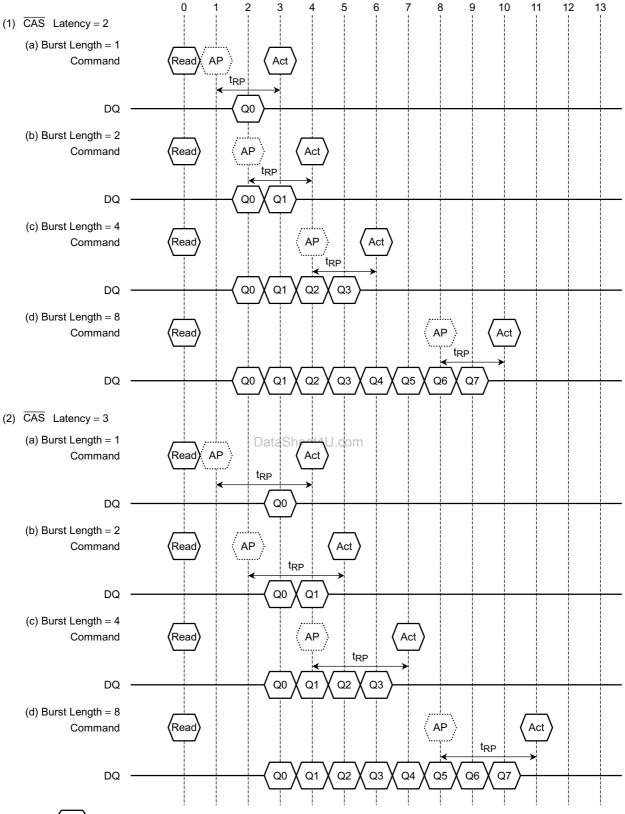

The Read command performs a Read operation to the bank designated by BS. The read data is issued sequentially synchronized to the positive edges of CLK. The length of read data (Burst Length), Addressing Mode and  $\overline{\text{CAS}}$  Latency (access time from  $\overline{\text{CAS}}$  command in a clock cycle) must be programmed in the Mode Register at power-up prior to the Write operation.

The A11 input is "Don't care" on the TC59SM708AFT/AFTL and the A9 and A11 inputs are "Don't care" on the TC59SM716AFT/AFTL.

et4U.com

www.DataSheet4U.com

DataShe

1-7 Read with Auto Precharge command

$$(\overline{RAS} = H, \overline{CAS} = L, \overline{WE} = H, BS = Bank, A10 = H, A0 \sim A9, A11 = Column Address)$$

The Read with Auto Precharge command automatically performs the Precharge operation after the Read operation. When the  $\overline{\text{CAS}}$  Latency = 3, the internal precharge starts two cycles before the last data is output. When the  $\overline{\text{CAS}}$  Latency = 2, the internal precharge starts one cycle before the last data is output (Figure 15). This command must not be interrupted by any other command.

The A11 input is "Don't care" on the TC59SM708AFT/AFTL and the A9 and A11 inputs are "Don't care" on the TC59SM716AFT/AFTL.

1-8 Mode Register Set command

$$(\overline{RAS} = L, \overline{CAS} = L, \overline{WE} = L, BS, A0\sim A11 = Register Data)$$

The Mode Register Set command programs the values of  $\overline{\text{CAS}}$  latency, Addressing Mode and Burst Length in the Mode Register. The default values in the Mode Register after power-up are undefined, therefore this command must be issued during the power-up sequence. Also, this command can be issued while all banks are in the idle state.

1-9 No-Operation command

$$(\overline{RAS} = H, \overline{CAS} = H, \overline{WE} = H)$$

The No-Operation command simply performs no operation.

1-10 Burst stop command

$$(\overline{RAS} = H, \overline{CAS} = H, \overline{WE} = L)$$

The Burst stop command is used to stop the burst operation. This command is valid during a Full Page Burst operation. During other types of Burst operation, the command is illegal.

1-11 Device Deselect command

$$(\overline{CS} = H)$$

DataSheet4U.com

The Device Deselect command disables the command decoder so that the  $\overline{RAS}$ ,  $\overline{CAS}$ ,  $\overline{WE}$  and Address inputs are ignored. This command is similar to the No-Operation command.

1-12 Auto Refresh command

$$(\overline{RAS} = L, \overline{CAS} = L, \overline{WE} = H, CKE = H, BS, A0~A11 = Don't care)$$

The Auto Refresh command is used to refresh the row address provided by the internal refresh counter. The Refresh operation must be performed 4096 times within 64 ms. The next command can be issued after  $t_{RC}$  from the end of the Auto Refresh command. When the Auto Refresh command is issued, All banks must be in the idle state. The Auto Refresh operation is equivalent to the  $\overline{CAS}$ -before- $\overline{RAS}$  operation in a conventional DRAM.

et4U.com

www.DataSheet4U.com

DataShe

1-13 Self Refresh Entry command

$$(\overline{RAS} = L, \overline{CAS} = L, \overline{WE} = H, CKE = L, BS, A0~A11 = Don't care)$$

The Self Refresh Entry command is used to enter Self Refresh mode. While the device is in Self Refresh mode, all input and output buffers (except the CKE buffer) are disabled and the Refresh operation is automatically performed. Self Refresh mode is exited by taking CKE "high" (the Self Refresh Exit command).

1-14 Self Refresh Exit command

$$(CKE = H, \overline{CS} = H \text{ or } CKE = H, \overline{RAS} = H, \overline{CAS} = H)$$

This command is used to exit from Self Refresh mode. Any subsequent commands can be issued after tRC from the end of this command.

1-15 Clock Suspend Mode Entry/Power Down Mode Entry command (CKE = L)

The internal CLK is suspended for one cycle when this command is issued (when CKE is asserted "low"). The device state is held intact while the CLK is suspended. On the other hand, when the device is not operating the Burst cycle, this command performs entry into Power Down mode. All input and output buffers (except the CKE buffer) are turned off in Power Down mode.

1-16 Clock Suspend Mode Exit/Power Down Mode Exit command (CKE = H)

When the internal CLK has been suspended, operation of the internal CLK is resumed by providing this command (asserting CKE "high"). When the device is in Power Down mode, the device exits this mode and all disabled buffers are turned on to the active state. Any subsequent commands can be issued after one clock cycle from the end of this command.

1-17 Data Write/Output Enable, Data Mask/Output Disable command (DQM = L/H or LDQM, UDQM = L/H) DataSheet4U.com

DataShe

During a Write cycle, the DQM or LDQM, UDQM signal functions as Data Mask and can control every word of the input data. During a Read cycle, the DQM or LDQM, UDQM signal functions as the control of output buffers.

The LDQM signal controls DQ0~DQ7 and the UDQM signal controls DQ8~DQ15.

DataSheet4U.com www.DataSheet4U.com

#### 2. Read Operation

Issuing the Bank Activate command to the idle bank puts it into the active state. When the Read command is issued after tRCD from the Bank Activate command, the data is read out sequentially, synchronized to the positive edges of CLK (a Burst Read operation). The initial read data becomes available after  $\overline{\text{CAS}}$  Latency from the issuing of the Read command. The  $\overline{\text{CAS}}$  latency must be set in the Mode Register at power-up. In addition, the burst length of read data and Addressing Mode must be set. Each bank is held in the active state unless the Precharge command is issued, so that the sense amplifiers can be used as secondary cache.

When the Read with Auto Precharge command is issued, the Precharge operation is performed automatically after the Read cycle, then the bank is switched to the idle state. This command cannot be interrupted by any other commands. Also, when the Burst Length is 1 and  $t_{RCD}$  (min), the timing from the  $\overline{RAS}$  command to the start of the Auto Precharge operation is shorter than  $t_{RAS}$  (min). In this case,  $t_{RAS}$  (min) must be satisfied by extending  $t_{RCD}$  (Figure 9, 15).

When the Precharge operation is performed on a bank during a Burst Read operation, the Burst operation is terminated (Figure 20).

When the Burst Length is full-page, column data is repeatedly read out until the Burst Stop command or Precharge command is issued.

### 3. Write Operation

Issuing the Write command after t<sub>RCD</sub> from the Bank Activate command, the input data is latched sequentially, synchronizing with the positive edges of CLK after the Write command (Burst Write operation). The burst length of the Write data (Burst Length) and Addressing Mode must be set in the Mode Register at power-up.

When the Write with Auto Precharge command is issued, the Precharge operation is performed automatically after the Write cycle, then the bank is switched to the idle state. This command cannot be interrupted by any other command for the entire burst data duration. Also, when the Burst Length is 1 and  $t_{RCD}$  (min), the timing from the  $\overline{RAS}$  command to the start of the Auto Precharge operation is shorter than  $t_{RAS}$  (min). In this case,  $t_{RAS}$  (min) must be satisfied by extending  $t_{RCD}$  (Figure 10, 16).

When the Precharge operation is performed in a bank during a Burst Write operation, the Burst operation is terminated (Figure 20).

When the Burst Length is full-page, the input data is repeatedly latched until the Burst Stop command or the Precharge command is issued.

When the Burst Read and Single Write mode is selected, the write burst length is 1 regardless of the read burst length.

DataShe

et4U.com

#### 4. Precharge

There are two commands which perform the Precharge operation: Bank Precharge and Precharge All. When the Bank Precharge command is issued to the active bank, the bank is precharged and then switched to the idle state. The Bank Precharge command can precharge one bank independently of the other bank and hold the unprecharged bank in the active state. The maximum time each bank can be held in the active state is specified as tRAS (max). Therefore, each bank must be precharged within tRAS (max) from the Bank Activate command.

The Precharge All command can be used to precharge all banks simultaneously. Even if banks are not in the active state, the Precharge All command can still be issued. In this case, the Precharge operation is performed only for the active bank and the precharged bank is then switched to the idle state.

#### 5. Page Mode

The Read or Write command can be issued on any clock cycle.

Whenever a Read operation is to be interrupted by a Write command, the output data must be masked by DQM to avoid I/O conflict. Also, when a Write operation is to be interrupted by a Read command, only the input data before the Read command is enable and the input data after the Read command is disabled.

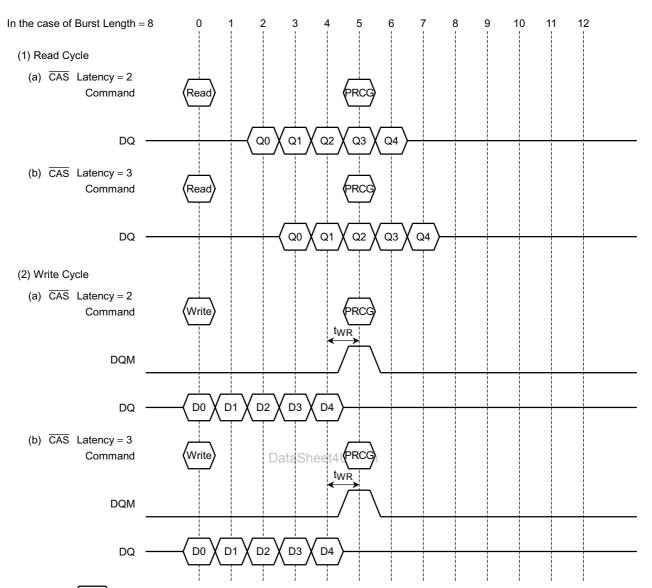

#### 6. Burst Termination

When the Precharge command is issued for a bank in a Burst cycle, the Burst operation is terminated. When the Burst Read cycle is interrupted by the Precharge command, read operation is disabled after clock cycle of ( $\overline{\text{CAS}}$  latency-1) from the Precharge command (Figure 20). When the Burst Write cycle is interrupted by the Precharge command, the input circuit is reset at the same clock cycle at which the Precharge command is issued. In this case, the DQM signal must be asserted "High" to prevent writing the invalid data to the cell array (Figure 20).

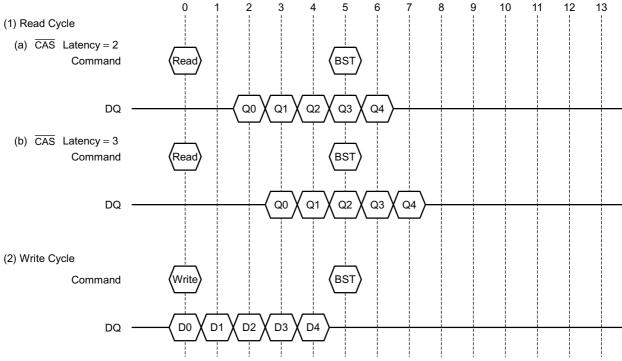

When the Burst Stop command is issued for the bank in a Full-page Burst cycle, the Burst operation is terminated. When the Burst Stop command is issued during Full-page Burst Read cycle, read operation is disabled after clock cycle of  $(\overline{CAS})$  latency-1) from the Burst Stop command. When the Burst Stop command is issued during a Full-page Burst Write cycle, write operation is disabled at the same clock cycle at which the Burst Stop command is issued. (Figure 19)

et4U.com

DataSheet4U.com

DataShe

#### 7. Mode Register Operation

The Mode register designates the operation mode for the Read or Write cycle. This register is divided into three fields; A <u>Burst Length field</u> to set the length of burst data, an <u>Addressing Mode selected bits</u> to designate the column access sequence in a Burst cycle, and a  $\overline{\text{CAS}}$  <u>Latency field</u> to set the access time in clock cycle.

The Mode Register is programmed by the Mode Register Set command when all banks are in the idle state. The data to be set in the Mode Register is transferred using the A0~A11 address inputs. The initial value of the Mode Register after power-up is undefined; therefore the Mode Register Set command must be issued before proper operation.

#### Burst Length field (A2~A0)

This field specifies the data length for column access using the A2~A0 pins and sets the Burst Length to be 1, 2, 4, 8, words, or full-page.

| A2 | A1 | Α0 | Burst Length |

|----|----|----|--------------|

| 0  | 0  | 0  | 1 word       |

| 0  | 0  | 1  | 2 words      |

| 0  | 1  | 0  | 4 words      |

| 0  | 1  | 1  | 8 words      |

| 1  | 1  | 1  | Full-Page    |

#### • Addressing Mode Select (A3)

The Addressing Mode can be one of two modes; Interleave mode or Sequential mode. When the A3 bit is 0, Sequential mode is selected. When the A3 bit is 1, Interleave mode is selected.

Both Addressing modes support burst length of 1, 2, 4 and 8 words. Additionally, Sequential mode supports the full-page burst.

| А3 | Addressing Mode Datas | Sheet4U.com |

|----|-----------------------|-------------|

| 0  | Sequential            |             |

| 1  | Interleave            |             |

DataShe

DataSheet4U.com www.DataSheet4U.com

• Addressing sequence of Sequential mode

A column access is performed by incrementing the column address input to the device. The address is varied by the Burst Length as shown in Table 2.

Table 2. Addressing sequence for Sequential mode

| DATA  | Access Address | Burst Length                                           |

|-------|----------------|--------------------------------------------------------|

| Data0 | n              | 2 wards (Address hits is AO)                           |

| Data1 | n + 1          | 2 words (Address bits is A0) not carried from A0 to A1 |

| Data2 | n + 2          | 4 words (Address bits is A1, A0)                       |

| Data3 | n + 3          | not carried from A1 to A2                              |

| Data4 | n + 4          | 8 words (Address bits is A2, A1, A0)                   |

| Data5 | n + 5          | not carried from A2 to A3                              |

| Data6 | n + 6          |                                                        |

| Data7 | n + 7          | J                                                      |

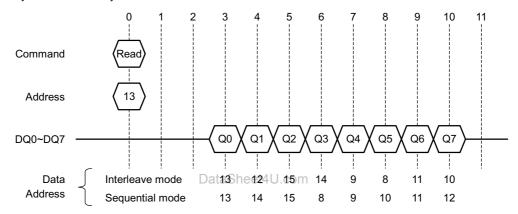

• Addressing sequence of Interleave mode

A column access is started from the input column address and is performed by inverting the address bits in the sequence shown in Table 3.

Table 3. Addressing sequence for Interleave mode

| DATA  |    |    |    | Acce | ess Ado | dress |    |    |    | Burst Length |

|-------|----|----|----|------|---------|-------|----|----|----|--------------|

| Data0 | A8 | A7 | A6 | A5   | A4      | АЗ    | A2 | A1 | A0 |              |

| Data1 | A8 | A7 | A6 | A5   | A4      | A3    | A2 | A1 | A0 | 2 words      |

| Data2 | A8 | A7 | A6 | A5   | A4      | A3    | A2 | A1 | A0 | - 4 words    |

| Data3 | A8 | A7 | A6 | A5   | A4      | А3    | A2 | A1 | Ā0 |              |

| Data4 | A8 | A7 | A6 | A5   | A4      | А3    | A2 | A1 | A0 | > 8 words    |

| Data5 | A8 | A7 | A6 | A5   | A4      | А3    | Ā2 | A1 | Ā0 |              |

| Data6 | A8 | A7 | A6 | A5   | A4      | А3    | A2 | A1 | A0 |              |

| Data7 | A8 | A7 | A6 | A5   | A4      | А3    | Ā2 | A1 | A0 | J            |

et4U.com

DataShe

| Addressing sequence example | (Burst Length = 8 | 8 and input address | s is 13.) |

|-----------------------------|-------------------|---------------------|-----------|

| DATA  |    | Interleave Mode |    |    |    |    |    |    |    | Sequential Mode | uential Mode |     |                                     |

|-------|----|-----------------|----|----|----|----|----|----|----|-----------------|--------------|-----|-------------------------------------|

| DATA  | A8 | A7              | A6 | A5 | A4 | А3 | A2 | A1 | A0 | ADD             |              | ADD |                                     |

| Data0 | 0  | 0               | 0  | 0  | 0  | 1  | 1  | 0  | 1  | 13              | 13           | 13  |                                     |

| Data1 | 0  | 0               | 0  | 0  | 0  | 1  | 1  | 0  | 0  | 12              | 13 + 1       | 14  |                                     |

| Data2 | 0  | 0               | 0  | 0  | 0  | 1  | 1  | 1  | 1  | 15              | 13 + 2       | 15  | calculated using A2, A1 and A0 bits |

| Data3 | 0  | 0               | 0  | 0  | 0  | 1  | 1  | 1  | 0  | 14              | 13 + 3       | 8   | not carry from                      |

| Data4 | 0  | 0               | 0  | 0  | 0  | 1  | 0  | 0  | 1  | 9               | 13 + 4       | 9   | A2 to A3 bit.                       |

| Data5 | 0  | 0               | 0  | 0  | 0  | 1  | 0  | 0  | 0  | 8               | 13 + 5       | 10  |                                     |

| Data6 | 0  | 0               | 0  | 0  | 0  | 1  | 0  | 1  | 1  | 11              | 13 + 6       | 11  |                                     |

| Data7 | 0  | 0               | 0  | 0  | 0  | 1  | 0  | 1  | 0  | 10              | 13 + 7       | 12  |                                     |

et4U.com

DataShe

### • CAS Latency field (A6~A4)

This field specifies the number of clock cycles from the assertion of the Read command to the first data read. The minimum values of  $\overline{CAS}$  Latency depends on the frequency of CLK. The minimum value must be set in this field.

| A6 | A5 | A4 | CAS Latency |

|----|----|----|-------------|

| 0  | 1  | 0  | 2 clock     |

| 0  | 1  | 1  | 3 clock     |

#### Test mode entry bit (A7)

This bit is used to enter Test mode and must be set to 0 for normal operation.

#### • Reserved bits (A8, A10, A11, BS0, BS1)

These bits are reserved for future operations. They must be set to 0 for normal operation.

#### • Single Write mode (A9)

This bit is used to select the write mode. When the A9 bit is 0, Burst Read and Burst Write mode are selected. When the A9 bit is 1, Burst Read and Single Write mode are selected.

| A9 | Write Mode                  |

|----|-----------------------------|

| 0  | Burst Read and Burst Write  |

| 1  | Burst Read and Single Write |

www.DataSheet4U.com

2000-02-08 39/49

DataSheet4U.com

#### 8. Refresh Operation

Two types of Refresh operation can be performed on the device: Auto Refresh and Self Refresh. Auto Refresh is similar to the  $\overline{\text{CAS}}$ -before- $\overline{\text{RAS}}$  refresh of conventional DRAMs and is performed by issuing the Auto Refresh command while all banks are in the idle state. By repeating the Auto Refresh cycle, each bank refreshed automatically. The Refresh operation must be performed 4096 times (rows) within 64 ms (Figure 11). The period between the Auto Refresh command and the next command is specified by tRC.

Self Refresh mode is entered by issuing the Self Refresh command (CKE asserted "low") while all banks are in the idle state. The device is in Self Refresh mode for as long as CKE is held "low". In Self Refresh mode, all input/output buffers (except the CKE buffer) are disabled to lower power dissipation (Figure 12).

In the case of 4096 burst Auto Refresh commands, 4096 burst Auto Refresh commands must be performed within 15.6 µs before entering and after exiting the Self Refresh mode.

In the case of distributed Auto Refresh commands, distributed Auto Refresh commands must be issued every  $15.6~\mu s$  and the last distributed Auto Refresh command must be performed within  $15.6~\mu s$  before entering the Self Refresh mode. After exiting from the Self Refresh mode, the refresh operation must be performed within  $15.6~\mu s$ .

### 9. Power Down Mode

When the device enters the Power Down mode, all input/output buffers (except CKE buffer) are disabled to lower power dissipation in the idle state. Power Down mode is entered by asserting CKE "low" while the device is not running a Burst cycle. Taking CKE "high" exit this mode. When CKE goes high, a No-operation command must be input at next CLK rising edge of CLK (Figure 13).

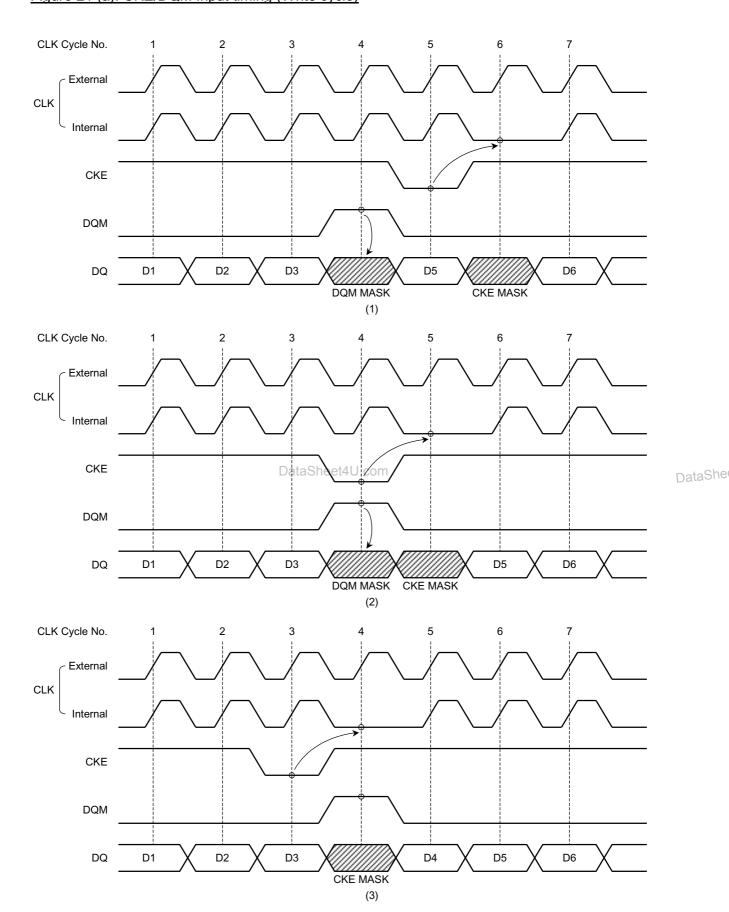

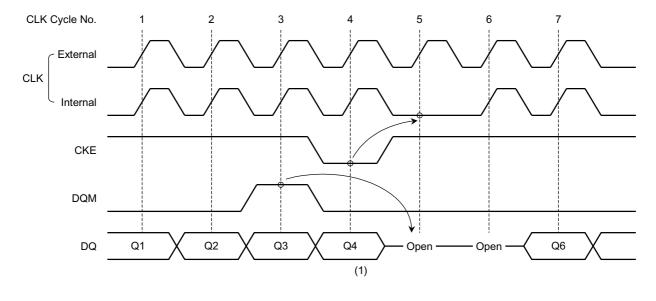

#### 10. CLK suspension and Input/Output Mask

When the device is running a Burst cycle, the internal CLK is suspended by asserting CKE "low" and the burst operation is frozen from the next cycle. A Read/Write operation is held intact until the CKE signal is taken "high".

The Output Disable/Write Mask signal (DQM) has two functions, controlling the output data in a Read cycle and performing word mask in a Write cycle. When the DQM is asserted "high" at the positive edge of CLK, the output data is disabled after two clock cycles in the case of a Read operation and the write data is masked at the same clock cycle in the case of a Write operation. The timing relations between the CKE timing and DQM are described in Figure 21 (a) and 21 (b).

DataShe

et4U.com

### Figure 15. Auto Precharge timing (Read cycle)

- Note) (Read) represents the Read with Auto Precharge command.

- AP represents the start of internal precharging.

- Act represents the Bank Activate command.

- When the Auto Precharge command is asserted, the period from the Bank Activate command to the start of internal precharging must be at least t<sub>RAS</sub> (min).

DataSheet4U.com www.DataSheet4U.com

DataShe

### Figure 16. Auto Precharge timing (Write cycle)

- Note) Write represents the Write with Auto Precharge command.

- AP represents the start of internal precharging.

- Act represents the Bank Activate command.

- When the Auto Precharge command is asserted, the period from the Bank Activate command to the start of internal precharging must be at least t<sub>RAS</sub> (min).

DataSheet4U.com www.DataSheet4U.com

DataShe

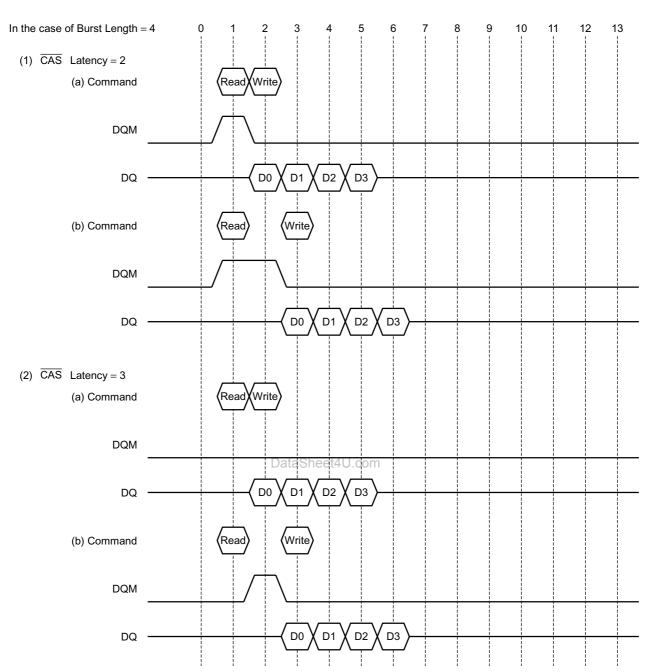

### Figure 17. Timing chart for Read-to-Write cycle

Note) • The output data must be masked by DQM to avoid I/O conflict.

DataSheet4U.com www.DataSheet4U.com

DataShe

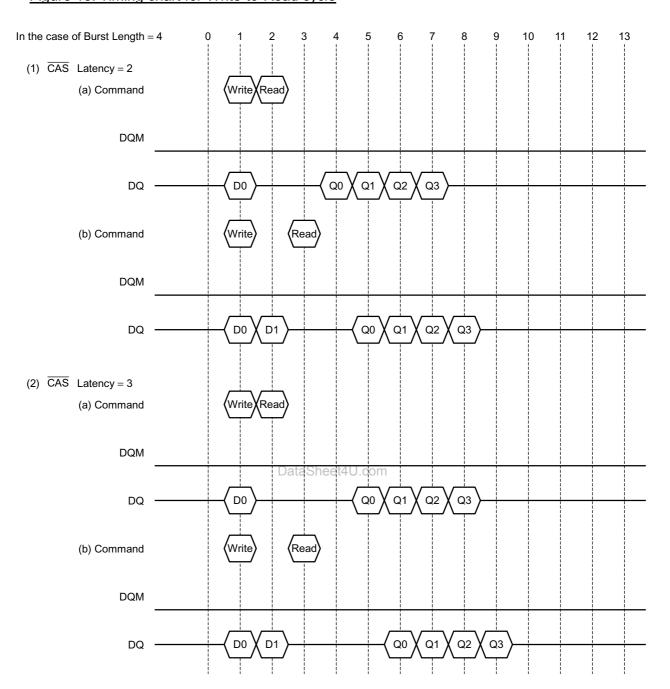

### Figure 18. Timing chart for Write-to-Read cycle

et4U.com

DataShe

### Figure 19. Timing chart for Burst Stop cycle (Burst stop command)

Note) • (BST) represents the Burst stop command.

et4U.com

DataSheet4U.com

DataShe

### Figure 20. Timing chart for Burst Stop cycle (Precharge command)

et4U.com

DataShe

Note) • (PRCG) represents the Precharge command.

## Figure 21 (a). CKE/DQM Input timing (Write cycle)

DataSheet4U.com

2000-02-08 47/49

www.DataSheet4U.com

## Figure 21 (b). CKE/DQM Input timing (Read cycle)

et4U.com

DataShe

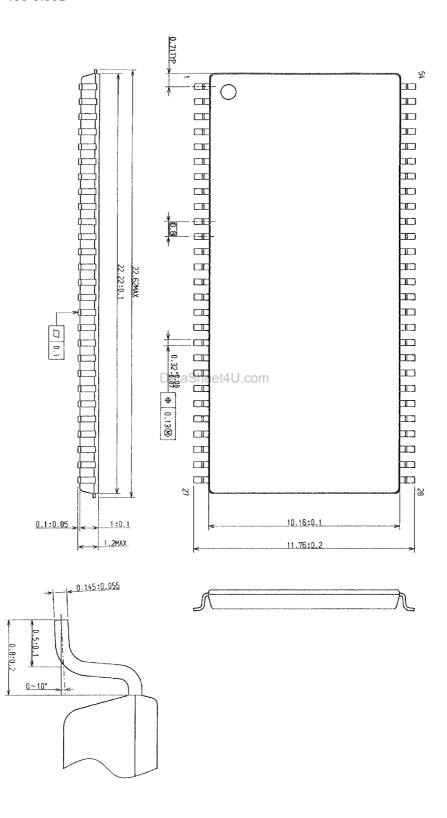

## **PACKAGE DIMENSIONS**

Unit: mm

TSOPII54-P-400-0.80B

et4U.com